Всем доброго времени суток! Сегодняшний мой пост посвящён цифровым микросхемам, которые имеют память. Подобно тому, как человек помнит события из своей жизни, так и эти микросхемы могут долго хранить заложенную в них информацию, а когда необходимо выдавать её.

Такими цифровыми микросхемами являются триггеры (англ. – Trigger или Flip-Flop). В отличие от простых логических микросхем, которые называют комбинационными (НЕ, И-НЕ, ИЛИ и другие) и их сигналы на выходе чётко соответствуют сигналам на входе, то триггеры относятся к последовательным или последовательностным микросхемам, уровень выходного напряжения которых, зависит от того в какой последовательности поступали сигналы на вход триггера. С помощью триггеров строят более сложные цифровые микросхемы.

Для сборки радиоэлектронного устройства можно преобрески DIY KIT набор по ссылке.

Сигналы, поступившие на вход триггера, могут храниться только до тех пор, пока на него подается напряжение питания. После каждого включения триггера на его выходах появляются случайные логические уровни напряжения. Триггеры обладают очень высоким быстродействием, сравнимым с задержками при переключении простейших логических элементов, однако объём хранимой информации мал. Один триггер может хранить только один сигнал или бит.

Внутреннее устройство триггера

Не вдаваясь в глубину схемотехники триггера, скажу сразу, что простейший триггер представляет собой схему из двух логических элементов, взаимодействуя между собой с помощью положительной обратной связи, которая обеспечивает нахождения выходов триггера в одном их двух логических состояний неограниченное время.

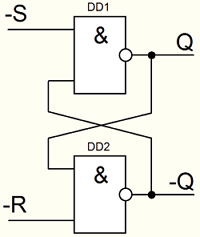

Схема триггерной ячейки на логических элементах (RS триггер).

Схема на рисунке выше представляет простейший триггер (или триггерная ячейка), который имеет два входа и два выхода. Входы триггера реагируют на низкий логический уровень: вход R – сброс (англ. Reset – сброс) и вход S – установка (англ. Set – установка), выходы: прямой Q (англ. Quit – выход) и инверсный –Q.

Как говорилось выше, входы триггера R и S реагируют на низкий логический уровень и сигналы на них должны поступать с некоторой разницей во времени. Опишем работу данной схемы. Когда на обоих входах триггера присутствует низкий логический уровень, то это никак не отразится на уровне напряжения на выходах. Когда на вход S поступит сигнал лог. 1, то на выходах Q будет лог. 0, а на –Q – лог. 1. Если теперь на вход R триггера поступит лог. 1, то выходные сигналы не изменятся. И наконец если изменить уровень сигнала на входе S с высокого на низкий уровень, то на выходе триггера Q будет лог. 1, а на –Q – лог. 0. Таким образом, для данной триггерной ячейки можно составить таблицу истинности.

Таблица истинности триггерной ячейки (RS триггер).

Триггеры для Standoff 2 — Есть ли смысл?

| Входы | Выходы | ||

| R | S | Q | -Q |

| 0 | 0 | Не определено | |

| 0 | 1 | 0 | 1 |

| 1 | 1 | Без изменений | |

| 1 | 0 | 1 | 0 |

Схемы с такой таблицей истинности называются RS триггерами. RS триггеры служат основой для многих динамических устройств: делители частоты, счётчики, регистры. Кроме вышеописанного RS триггера существует ещё несколько типов триггеров, которые отличаются методом управления, входными и выходными сигналами. Все современные триггеры объединены в серии цифровых микросхем:

- RS триггеры – самый простой и редко используемый триггер, имеет обозначение ТР;

- JK триггер – имеет сложное управление, обозначение ТВ;

- D триггер – самый распространённый и имеет сложность среднюю, обозначение ТМ;

▍ Машина для голосования

Первая из сегодняшних поделок зажигает светодиод только при условии, что одновременно нажаты две кнопки. Любые две из трёх, либо все три. Таков принцип голосования: решение принято, если за него проголосовало большинство.

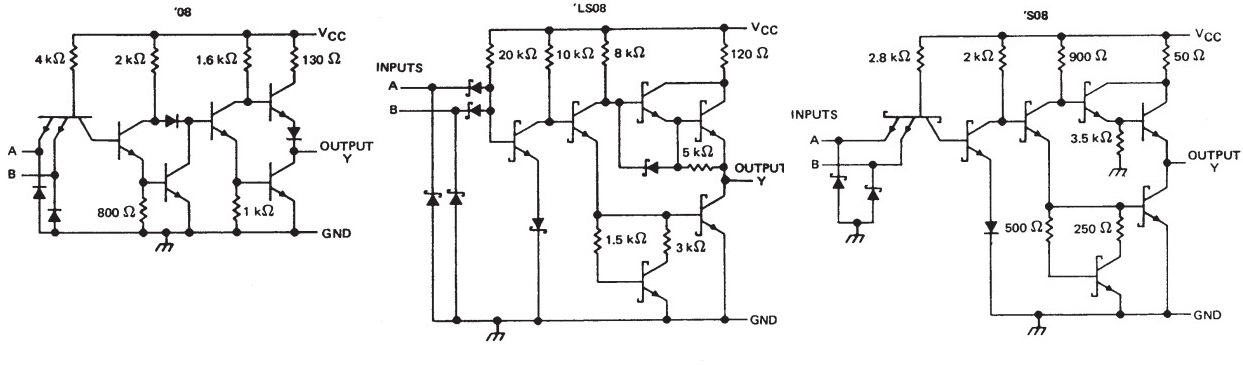

Схема использует три логических элемента 2И микросхемы 74LS08 , она же К555ЛИ1 . Входы каждого из них обрабатывают три возможных пары из трёх кнопок — первая и вторая, вторая и третья, первая и третья.

74 и 555 являются сериями микросхем ТТЛ — транзисторно-транзисторной логики. В 7408 используются транзисторы структуры NPN и обычные кремниевые диоды. В 74S08 применены диоды Шоттки и транзисторы Шоттки. В 74LS08 отказались от многоэмиттерных транзисторов и фактически вернулись к диодно-транзисторной логике ДТЛ, при сохранении традиционного названия ТТЛ.

Транзистор Шоттки представляет собой комбинацию биполярного транзистора и диода Шоттки. Входной ток, который управляет базой транзистора, имеет два пути: один путь в базу, а другой путь через диод Шоттки в коллектор. Когда транзистор открыт, на его переходе база-эмиттер будет около 0,6 В. Как правило, напряжение коллектора будет выше, чем напряжение базы, и диод Шоттки будет смещён в обратном направлении.

Если входной ток увеличивается, то напряжение коллектора падает ниже напряжения базы, и диод Шоттки начинает проводить и шунтировать часть управляющего тока базы в коллектор. Транзистор сконструирован таким образом, что его напряжение насыщения коллектора меньше, чем напряжение база-эмиттер (примерно 0,6 В) за вычетом прямого падения напряжения на диоде Шоттки (примерно 0,2 В).

Следовательно, избыточный входной ток отводится от базы, и транзистор никогда не переходит в режим насыщения, после которого требуется время для того, чтобы рассосались неосновные носители заряда (время восстановления). Благодаря этому, транзистор Шоттки позволяет создать более быстродействующие микросхемы, чем построенные на обычных транзисторах.

Входы элементов 2И подтянуты к земле резисторами 1 кОм, а нажатая кнопка подтягивает соответствующие входы к плюсу питания.

С выхода каждого элемента 2И логический сигнал поступает на вход элемента 3ИЛИ микросхемы CD4075 . Получается, что выход CD4075 включит светодиод и откроет транзистор, включающий зуммер, когда хотя бы на один из трёх входов поступит логическая единица. То есть когда нажаты две или три кнопки.

CD4075 — это уже микросхема не ТТЛ или ДТЛ, а КМОП (СMOS) , — комплементарной металл-оксид-полупроводник — логики. Это внутренняя структура микросхемы без резисторов, на комплементарных парах P-канальных и N-канальных полевых транзисторов с изолированным затвором. Входы микросхемы, а, соответственно, затворы транзисторов, защищены от статических разрядов и перенапряжения диодами.

В статье про другую КМОП микросхему серии К561, или CD40, мы уже видели такую, на первый взгляд, странную внутреннюю логику, где каждый логический элемент, в том числе буфер-повторитель, является инвертирующим.

На самом деле тут нет ничего удивительного. Транзисторный каскад с общим эмиттером или общим истоком, в том числе двухтактный, как в микросхеме СMOS логики, инвертирует сигнал. Высокий логический уровень на входе каскада создаёт низкий уровень на выходе, и наоборот.

Потому буфер реализован двумя последовательными инверторами, а логический элемент с неинвертирующим выходом — инвертором после инвертирующего.

Недостатком этого устройства на случай, если бы оно применялось для реального голосования, является отсутствие фиксации результата. Здесь как раз пригодился бы триггер.

▍ Реле времени на ждущем мультивибраторе

Следующая конструкция — также не триггер, а моностабильный мультивибратор, или одновибратор. Он выдаёт не последовательность импульсов, а всего один импульс определённой длины при поступлении импульса на вход.

Если коснуться сенсора, подключённого ко входу запуска — ноге 2 интегрального таймера NE555 , его выход — вывод 3 — переходит в состояние высокого логического уровня. В результате гаснет «дежурный» красный светодиод и загораются 5 белых осветительных.

Также закрывается встроенный в микросхему транзистор, шунтировавший электролитический конденсатор С3. Когда он зарядится через резистор R2 и подстроечный резистор VR1 до двух третей напряжения питания, сработает встроенный компаратор 2, и сбросит встроенный триггер таймера NE555.

Яркие белые светодиоды погаснут, и загорится красный дежурный светодиод. Одновременно с этим активируется выход 7 с открытым коллектором, через который практически моментально разряжается электролитический конденсатор С3.

Конденсаторы C1 и C2 защищает входы компараторов от помех. Время зарядки конденсатора С3, а, соответственно, яркого белого свечения, зависит от его ёмкости и положения бегунка переменного резистора, и в данной схеме может составлять от 3 до 130 секунд. Такое устройство можно использовать для освещения шкафа, электрического щитка или подсобного помещения.

В предыдущей статье мы собирали гитарный эффект, одним из узлов которого является электронный переключатель на транзисторном триггере Т-типа. При каждом нажатии кнопки без фиксации он переключается между двумя фиксированными состояниями. А в интегральном таймере NE555 имеется RS-триггер и два компаратора.

Компаратором называется схемотехнический узел, на выходе которого высокий логический уровень, если напряжение на неинвертирующем входе выше, чем на инвертирующем, и низкий, если наоборот.

Выход RS-триггера переключается в состояние высокого логического уровня при высоком уровне на входе S — Set, установка . И, соответственно, в состояние низкого логического уровня выход триггера переходит при высоком уровне на входе R — Reset, сброс.

Триггеры

Триггер — это устройство последовательного типа с двумя устойчивыми состояниями равновесия, предназначенное для записи и хранения информации. Под действием входных сигналов триггер может переключаться из одного устойчивого состояния в другое. При этом напряжение на его выходе скачкообразно изменяется. Как правило, триггер имеет два выхода: прямой и инверсный. Число входов зависит от структуры и функций, выполняемых триггером. По способу записи информации триггеры делят на асинхронные и синхронизируемые (тактируемые). В асинхронных триггерах информация может записываться непрерывно и определяется информационными сигналами, действующими на входах в данный момент времени. Если информация заносится в триггер только в момент действия так называемого синхронизирующего сигнала, то такой триггер называют синхронизируемым или тактируемым. Помимо информационных входов тактируемые триггеры имеют тактовый вход синхронизации. В цифровой технике приняты следующие обозначения входов триггеров: S — раздельный вход установки в единичное состояние (напряжение высокого уровня на прямом выходе Q);

R — раздельный вход установки в нулевое состояние (напряжение низкого уровня на прямом выходе Q);

D — информационный вход (на него подается информация, предназначенная для занесения в триггер);

C — вход синхронизации;

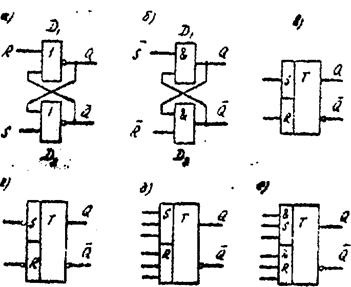

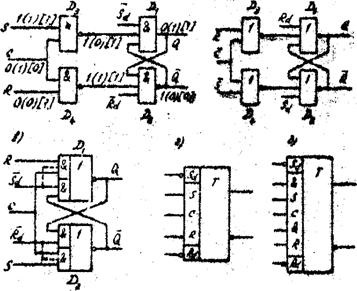

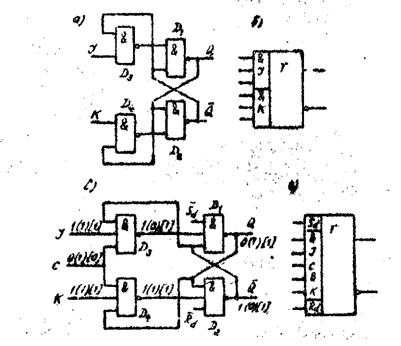

Т — счетный вход. Наибольшее распространение в цифровых устройствах получили RS-триггер с двумя установочными входами, тактируемый D-триггер и счетный Т-триггер. Рассмотрим функциональные возможности каждого из них. Асинхронный RS-триггер. В зависимости от логической структуры различают RS-триггеры с прямыми и инверсными входами. Их схемы и условные обозначения приведены на рисунке. Триггеры такого типа построены на двух логических элементах 2ИЛИ-НЕ — триггер с прямыми входами (а), 2И-НЕ — триггер с инверсными входами (б).

Рисунок 1

Выход каждого из элементов подключен к одному из выходов другого элемента. Здесь приведены таблицы истинности для каждого из этих триггеров

| S | R | Q t | -Q t | Q t+1 | -Q t+1 | S | R | Q t | -Q t | Q t+1 | -Q t+1 |

| 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 | 1 | 0 | 1 | 0 | 0 | 1 | 0 | 1 |

| 0 | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 1 | * | * |

| 1 | 1 | 0 | 1 | * | * | 1 | 1 | 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | * | * |

| 1 | 1 | 1 | 0 | * | * | 1 | 1 | 1 | 0 | 0 | 1 |

В таблицах (Q t и -Q t обозначают уровни, которые были на выходах триггера до подачи на его входы так называемых активных уровней. Активным. называют логический уровень, действующий на входе логического элемента и однозначно определяющий логический уровень выходного сигнала (независима от логических уровней, действующих на остальных входах). Для элементов ИЛИ-НЕ за активный уровень принимают высокий уровень, а для элементов И-НЕ — низкий уровень. Уровни, подача которых на один из входов не приводит к изменению логического уровня на выходе элемента, называют пассивными. Уровни Q t+1 и -Q t+1 обозначают логические уровни на выходах Триггера после подачи информации на его входы. Для триггера с прямыми входами Q t+1 =1 при S=1 и R=0; Q t+1 =0 при S=0 и R=1; Qt+1= Qt при S=0 и R=0. При R=S=1 состояние триггера будет неопределенным, так как во время действия информационных сигналов Логические уровни на выходах триггера одинаковы (Q t+1 =-Q t+1 =0), а после окончания их действия триггер может равновероятно принять любое из устойчивых состояний. Поэтому такая комбинация является запрещенной (и может вывести триггер из строя). Режим S=1, R=0 называют режимом записи 1 (так как Q t+1 =1); режим S=0 и R=1 — режимом записи 0. Режим S=0, R=О называется режимом хранения информации, так как информация на выходе остается неизменной. Для триггера с инверсными входами режим записи логической 1 реализуется при -S=0, -R=1, режим записи логического 0 — при -S=1, -R=0. При -S=-R=1 обеспечивается хранение информации. Комбинация S=R=0 является запрещенной. Следует, однако, отметить, что самостоятельно RS-триггеры в устройствах цифровой техники практически не используются из-за их низкой помехоустойчивости Тактируемый D-триггер. Он имеет информационный выход и вход синхронизации. Одна из возможных структурных схем однотактного D-триггера и его условное обозначение показаны на рисунке.

Рисунок 2 Если уровень сигнала на входе C= 0, состояние триггера устойчиво и не зависит от уровня сигнала на информационном входе. При этом на входы RS-триггера с инверсными входами (элементы 3 и 4) поступают пассивные уровни (-S=-R=1). При подаче на вход синхронизации уровня С=1 информация на прямом выходе будет повторять информацию, подаваемую на вход D. Таким образом, при C=0 Q t+1 =Q t , C=1 Q t+1 =D). Таблица истинности тактируемого D-триггера имеет вид:

| D | C | Q t+1 |

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

Здесь Q t означает логический уровень на прямом выходе до подачи импульса синхронизации, а Q t+1 — логический уровень на этом выходе после подачи импульса синхронизации. На рисунке 3 изображены временные диаграммы тактируемого D-триггера. В таком триггере происходит задержка сигнала на выходе по отношению к сигналу, поданному на вход. на время паузы между синхросигналами. Для устойчивой работы триггера необходимо, чтобы в течение синхроимпульса информация на входе была неизменной. Тактируемые D-триггеры могут быть с потенциальным и динамическим управлением. У первых из них информация записывается в течение времени, при котором уровень сигнала С=1. В триггерах с динамическим управлением информация записывается только в течение перепада напряжения на входе синхронизации. Динамические входы изображают на схемах треугольником. Если вершина треугольника обращена в сторону микросхемы, то триггер срабатывает по фронту входного импульса, если от нее — по срезу. Еще в схемах вы встретите / и обозначения первое соответственно фронт второе спад. В таком триггере информация на входе может быть задержана на один такт по отношению к входной информации.

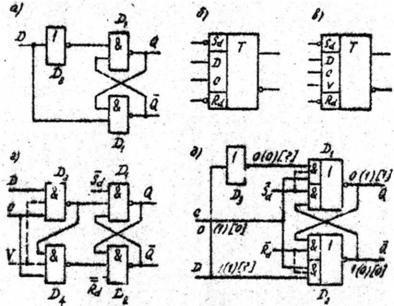

Рисунок 3 Счетный Т-триггер рисунок 4,а. Его называют также триггером со счетным входом. Он имеет один управляющий вход Т и два выхода Q и -Q. Информация на выходе такого триггера меняет свой знак на противоположный при каждом положительном (или при каждом отрицательном) перепаде напряжения на входе. Триггер такого типа может быть создан на базе тактируемого D-триггера, если его инверсный выход соединить с информационным входом (рис 4,б). Как видно из диаграммы на Рисунке 4,в, частота сигнала на выходе Т-триггера в два раза ниже частоты сигнала на входе, поэтому такой триггер можно использовать как делитель частоты и двоичный счетчик. В сериях выпускаемых микросхем есть также универсальные JK-триггеры. При соответствующем подключении входной логики JK-триггер может выполнить функции триггера любого другого типа.

GIG

GIG  Опубликована: 2005 г.

Опубликована: 2005 г.  0

0  0

0

![]()

Вознаградить Я собрал 0 0

Вознаградить Я собрал 0 0

Триггеры

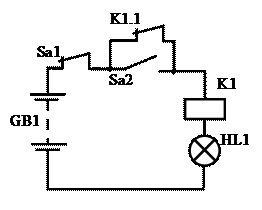

Триггер — электронная схема, имеющая несколько устойчивых состояний, сохраняющихся длительное время (пока включено электропитание схемы). Соответственно триггеры могут выполнять функцию элементов памяти. В цифровой технике используются бистабильные триггеры с двумя устойчивыми состояниями, которые кодируют значения логических «0» и «1». Триггеры могут быть построены на дискретных элементах (транзисторные каскады) и на логических элементах — цифровые триггеры. Также триггер может быть представлен в виде электромеханической аналогии (релейной схемы).

1 Классификация триггеров.

Триггеры различаются по логике работы и по способу приема и запоминания информации. Ниже представлена классификация триггеров, предложенная в книге Е.Угрюмова «Цифровая схемотехника». В ней выделены наиболее популярные типы триггеров, однако количество их разновидностей гораздо больше.

а) По логике работы:

1) RS — с раздельными входами записи «1» — «установки» (вход S) и записи «0» -«сброса» (сигнал R).

2) D — триггер задержки информационного сигнала (Delay).

3) T — тактируемый (Tact) или счетный триггер.

4) JK — универсальный триггер.

5) комбинированный — например, RST — тактируемый со входами «установки» и «сброса».

6) со сложной логикой — с группами входов, связанных логическими зависимостями. Например, JK-триггер с тремя входами J и тремя K, связанными конъюнкцией: (J1*J2*J3) и (K1*K2*K3).

б) По способу приема информации:

1) Асинхронные (нетактируемые) — переход в новое состояние происходит по изменению состояния управляющих (информационных) входов.

2) Синхронные (тактируемые) — переход в новое состояние под воздействием информационных входов происходит по только сигналу на специальном тактовом (синхронизации) входе (С / CLK / CLOCK).

Примечание: у реальных триггеров наряду с синхронизируемыми информационными входами сохраняют асинхронные информационные входы, чтобы обеспечить асинхронную установку или сброс триггера при реинициализации системы («сброс» или включение питания).

— Синхронные управляемые уровнем — при одном уровне тактового сигнала триггер воспринимает состояние управляющих входов, а при другом — не воспринимает и остается в одном состоянии, сохраняя записанную в него информацию. Типичный триггер управляемый уровнем — «триггер-защелка» (latch).

— Синхронные управляемые фронтом — При управлении фронтом переходы из состояния в состояние происходят по фронту тактового сигнала.

в) По внутренней структуре:

1) Одноступенчатые: в их внутренней структуре одна запоминающая схема, которая переключает свое состояние (запоминает данные) под влиянием управляющих сигналов. По одноступенчатой схеме строятся асинхронные триггеры и синхронные управляемые уровнем.

2) Двухступенчатые (или многоступенчатые) триггеры состоят из двух одноступенчатых триггеров. При переключении двухступенчатого триггера сначала переключается первая, а только следом — вторая. Это позволяет записывать данные только по фронту синхроимпульса, не реагируя на изменения на информационных входах в течении синхроимпульса. Т.е. по многоступенчатой схеме строятся синхронные управляемые фронтом триггеры. Это наиболее применяемый сегодня тип триггеров.

2 Структура триггера.

Триггеры состоят из двух блоков: схемы памяти (фиксатора) и схемы управления.

Электрически элемент памяти любого триггера это схема с положительной обратной связью. В частности, фиксатор цифрового триггера представляет собой два соединенных «крест-накрест» элемента НЕ (см. Рисунок 2, а).

Если на выходе одного элемента НЕ установилась «1», то она попадет на вход второго элемента НЕ и на его выходе будет «0», который, в свою очередь попадет на вход первого элемента НЕ и удержит на его выходе «1». Таким образом схема находится в устойчивом состоянии, которое будет сохраняться бесконечно долго — пока на схему памяти подано электропитание. Если же на выходе первого элемента изначально установился «0», то на выходе второго элемента будет «1», т.е. схема памяти переключится в противоположное состояние.

Если принять выход одного из этих элементов (допустим первого по описанию, приведенному выше) как выход всей схемы, то в первом из описанных устойчивых состояний схема памяти запомнит «1», а во втором запомнит «0». Выход второго элемента НЕ всегда будет в противоположном состоянии относительно выхода — его называют инверсным выходом. Выход (или «прямой» выход) обозначают Q. «Инверсный» выход обозначают nQ.

Схема из двух инвертеров не позволяет переключать ее из одного состояния в другое. Чтобы выполнить это, элементы НЕ заменяют элементами И-НЕ или ИЛИ-НЕ. Соответственно у схемы памяти появляются два входа, один из которых (этот вход называют входом «установки» — SET или S) выполняет переключение схемы в состояние «1» на выходе, а другой (этот вход называют входом «сброса» — RESET или R) — в состояние «0» не выходе.

Рассмотрим работу схемы с элементами ИЛИ-НЕ. Входы SET и RESET будут иметь активный уровень «1» и неактивный «0». Когда на входы R и S подан неактивный уровень логического «0» значение на выходе будет непредсказуемым — оно установится случайным образом при включении электропитания. Если для вышерассмотренной схемы на вход первого элемента ИЛИ-НЕ подать «1», то на выходе Q установится «0», а на nQ -«1», т.е. триггер запомнит «0» и будет сохранять это значение, даже если вход перейдет в неактивное состояние «0». В соответствии с таким действием данный управляющий вход называют R (Reset или Сброс). Если же «1» подать на второй вход, то на выходе Q установится и будет «запомнена» логическая «1» (nQ = 0), которая сохранится при переходе входа S в неактивное состояние «0». Соответственно этот вход называют S (Set или Установка).

Есть две важных особенности использования элемента памяти:

1. Если на входы R и S нельзя одновременно подать активные сигналы, фиксатор перейдет в состояние, когда на обоих выходах будет «1». Такое состояние считается недопустимым, так как на выходах Q и nQ должно быть противоположное значение. Кроме того, при снятии активных уровней с обоих входов R и S одновременно, невозможно предсказать, в какое состояние переключится элемент памяти.

2. Переключения фиксатора — «запоминание» — происходит в момент перехода управляющего сигнала R или S в активный уровень, и после этого, элемент памяти не изменяет своего состояния вне зависимости от того сохранился ли активный уровень на входе R или S или опять стал пассивным.

Аналогично описанной схеме работает и схема памяти на базе элементов И-НЕ. Разница только в полярности управляющих сигналов: в данном случае активным уровнем управляющих сигналов будет «0» и они будут соответственно называться nR и nS.

Описанная выше схема памяти является простейшим триггером — его называют триггером RS-типа или RS-триггером. RS-триггер достаточно неудобен в управлении, но может быть усовершенствован и преобразован в другие типы триггеров путем подключения дополнительной схемы управления. Таким образом RS-триггер основа большинства триггеров других типов.

Данная схема памяти имеет два независимых управляющих входа R и S, записывающих в нее «0» и «1» соответственно.

Однако использование только входов R и S не всегда удобно и сильно ограничивает возможности по запоминанию значений и по использованию триггеров в последовательностных схемах. Поэтому добавляют схему управления, которая преобразует более сложные комбинации управляющих сигналов, в том числе последовательности сигналов, в описанные сигналы R и S. Схема управления задает как логику (правила реакции на входные сигналы) работы триггера, так и способ приема информации триггером.

3. Асинхронные и синхронные управляемые фронтом триггеры

3.1. RS-триггеры.

Функционирование и внутренняя схема асинхронного RS — триггера соответствует описанной выше схеме памяти. Данный тип триггера фактически не имеет схемы управления на входе.

Синхронные RS — триггеры с управлением уровнем имеют вход синхронизации (С), сигнал на котором разрешает управление с информационных входов, пока находится в активном состоянии. Входные информационные сигналы «пропускаются» через логические вентили И (для схемы на базе элементов ИЛИ-НЕ, активный уровень (С) = 1) или через вентили ИЛИ (для схемы на базе элементов И-НЕ, активный уровень (С) = 0).

Характерной особенностью триггерных схем, управляемых уровней синхроимпульса, является то, то изменение уровней информационных сигналов в течение действия синхроимпульса приводит к изменению состояния триггера. Если по фронту синхросигнала в триггер было занесено значение «1», и далее в течение удержания активного уровня синхросигнала C информационные сигналы приняли значения R =1, S =0, то это приводит к переключению триггера в состояние «0». Следовательно, для обеспечения работы триггера сигналы R и S должны оставаться неизменными в течении активного уровня синхроимпульса, а изменяться в течение паузы между синхроимпульсами.

Синхронный RS-триггер с управлением по фронту построен по многоступенчатой схеме, описанной ниже.

RS-триггеры редко используются как самостоятельные элементы, но, как говорилось выше, являются элементом памяти (фиксатором) в составе других типов триггеров.

3.2. D-триггеры.

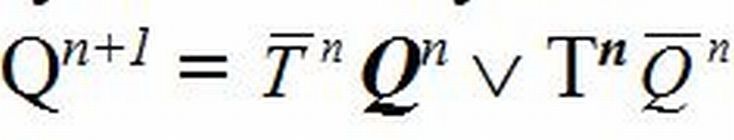

Для расширения функциональности к D-триггеру можно добавить вход разрешения V. При активном уровне (в данном случае «1») на данном входе триггер работает в вышеописанном режиме, при V = «0», триггер не реагирует на входы С и D. Поведение DV-триггера описывается формулой Qn+1 = DnVn Qn .

Второй тип, наиболее часто используемый — D-триггер с управлением по фронту синхросигнала, так называемый FLIP-FLOP. Данные записываются в него в момент перепада синхросигнала и сохраняются неизменными до следующего фронта. Такие триггеры строятся по двухступенчатой схеме и будут описаны ниже.

D-триггер является одним из самых широко используемых типов. Такие триггеры выпускаются отдельные микросхемы, а также являются базовыми структурными элементами многих ПЛИС. Несколько D-триггеров, с объединенными тактирующими входами образуют многоразрядные регистры: синхронные регистры (управление по уровню) или регистры-защелки (управление по фронту).

3.3. Т-триггеры.

Т -триггер представляет собой схему с одним логическим входом Т. Так как этот триггер работает в режиме учета импульсов на входе, его иногда называют счетным триггером (триггером со счетным входом). Т -триггер изменяет свое состояние на противоположное после воздействия импульса, поступающего на вход Т, т.е. его функционирование описывается формулой:

Схема простейшего Т -триггера с элементами задержки и в цепях обратной связи приведена ниже (см. Рисунок 5). Элементы задержки обеспечивают надежноепереключение триггера, причем время задержки tз на этих элементах должно быть больше длительности синхроимпульса на входе Т

Пусть Q = 1, Q`= 0. Поступающий на счетный вход импульс приводит к появлению нулевого сигнала на выходе элемента D4 (на его входах — две «1») и последовательной установке сигналов Q = 1, Q`= 0, т.е. к опрокидыванию триггера в нулевое состояние. При этом сигнал на входе D3 не изменяется, так как на его входе в течение tз действует нулевой сигнал, поступающий с выхода Q` через элемент задержки D5.

После окончания действия счетного импульса сигналы на выходах элементов D3 и D4 принимают единичные значения, а на вход D3 через элемент задержки D5 поступает разрешающий уровень с выхода Q`. В результате следующий счетный импульс перебросит триггер в исходное состояние.

Элементы D5 и D6 обеспечивают задержку появления сигналов обратной связи с тем, чтобы в течение действия счетного импульса не происходило многократного переключения триггера. В интегральных триггерах роль элементов задержки могут выполнять либо логические элементы, либо специальные полупроводниковые приборы с накоплением заряда. Однако, в силу жестких ограничений на длительность импульса на счетном входе и сложности реализации элементов задержки, Т-триггеры на базе RS-триггера с управлением уровнем синхросигнала почти не используются, а применяются триггеры с управлением по фронту синхросигнала.

ТV-триггер является разновидностью Т-триггера с дополнительным входом разрешения счета. Принцип его работы аналогичен DV-триггеру, описанному выше.

JK -триггер похож на RS — триггер (вход J эквивалентен входу S, а вход К — входу R), но не имеет запрещенного состояния К®=1, J(S)=1. При условии J=K=1 триггер осуществляет инверсию предыдущего состояния, а при остальных комбинациях входных сигналов функционирует в соответствии с таблицей истинности RS -триггера.

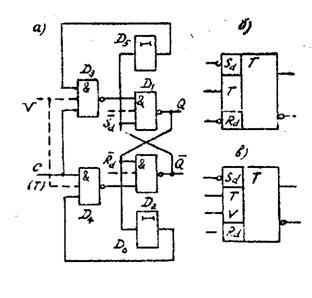

JK -триггер можно получить из RS -триггера, связав выходы триггера с его входами обратной связью. При этом схема управления должна быть построена таким образом, чтобы на входах R и S единичные сигналы одновременно не появлялись. Тогда при J = K =1 схема управления принуждает триггер работать в режиме переключения (счетный режим), так как, благодаря связи с выхода на вход, учитывается предшествующее состояние схемы, и сигнал направляется на соответствующий вход RS -триггера, вызывая его переключение.

Принципиально можно построить асинхронный JK -триггер (см. Рисунок 6 а), но они очень неустойчивы практического применения не находят: для нормальной работы асинхронного триггера в счетном режиме длительность управляющих сигналов не должна превышать времени переключения триггера, что очень сложно обеспечить на практике. В противном случае схема будет непрерывно переходить из одного состояния в другое, пока хотя бы один из сигналов не станет равным нулю.

Синхронный вариант JK -триггера с управлением уровней синхроимпульса получается из асинхронного путем добавления входа для подачи синхроимпульсов (Рисунок 6.в). В этой схеме занесение информации в триггер происходит при поступлении синхроимпульса. Максимальная длительность синхроимпульса должна быть чуть меньше, чем задержка в цепочке D1(D2)+D4(D3). Превышение этой величины вызывает появление ложного сигнала на выходе элемента D4(D3), что может привести к повторному переключению триггера. С другой стороны, длительность синхроимпульса ограничена по минимуму задержкой цепочки D1+D2, чтобы успел переключиться триггер. Чтобы выполнить эти условия на практике потребуется подбирать задержки элементов (причем, у D3 и D4 они должны быть больше чем у D1 и D2) и длительность синхроимпульса. Учитывая большие разбросы временных параметров, выполнить все условия на практике не представляется возможным. Поэтому рассмотренные синхронные JK -триггера также как и асинхронные на практике фактически нереализуемы. Работоспособность JK -триггеров обеспечивается только в схемах, управляемых фронтом (срезом) синхроимпульса.

JK-триггер

Является самым универсальным электронным элементом. В этих устройствах присутствуют:

- Входы «J» и«K» в качестве информационных. При этом «J» — обычный вход «S», а «K» — вход «R».

- «С» — вход динамический.

- «R» и «S» статические.

JK устройство работает по принципу перехода из одного состояния в другое, но с учетом единицы времени. Также существует разность при подаче сигнала на вход синхронизации. Иными словами, если на оба входа JK подать логическую 1, то на его выходах появится прямо противоположное значение. Но при этом устройство не воспримет наличие двух 1 единиц как ошибку.

В зависимости от назначения, в данном триггере может использоваться так называемый фронт (передний или задний). В этом случае устройство считается синхронным, а его состояние определяется актуальным положением логических чисел. При расчете рабочего состояния элемента также учитывается возможность одновременного использования устройства в качестве T или D триггера. В этом случае учитывается параметр временного интервала поступления сигнала, какое напряжение будет получено при выходе и устойчивость состояния элемента. Информатика часто использует этот элемент в качестве универсального устройства контроля состояния устойчивой работы простых логических функций. Далее дана диаграмма работы устройства.

Симметричный

Симметричный триггер относится к особому виду элементов. Он создается на транзисторах и является усилителем постоянного тока двухкаскадного типа. Работает устройство за счет использования транзисторов с полностью идентичными параметрами.

Принцип работы следующий:

- При подаче напряжения на устройство, транзистор VT1 считается открытым. Напряжение его коллектора равняется 0.

- В этот момент транзистор VT2 закрыт. Его коллектор имеет положительное напряжение.

- Для осуществления перехода из одного состояния в другое используется импульс напряжение. Этот импульс создается конденсатором.

- При появлении импульса транзисторы меняют свое состояние.

При смене положения транзисторов создается перепад напряжения, и оно значительно снижается.

В схемах симметричных триггеров основным элементом является система запуска. Она может отличаться по способу управления и месту, с которого поступил пусковой импульс.

- Раздельное управление. Предполагает подачу напряжения на определенный вход триггера. При таком управлении элемент считается RS-триггером.

- Общее или счетное управление. Напряжение подается на общий входной контакт. При таком подключении, устройство схоже по параметрам с Т-триггером.

Место поступления импульса может быть от коллектора или базы транзистора. При таких схемах подключения существует вероятность появления ложного или вторичного сигнала. Он отсекается путем подключения диода.

Основным недостатком симметричных элементов является полная зависимость от времени поступления импульсного сигнала и его длительности. Если длительность недостаточная, импульс не успеет открыть транзистор, а значит не произойдет закрытие второго транзистора.

Такие устройства используются в устройствах учета импульсов, генераторах частоты, переключателях радиоэлектронных цепей.

Триггеры на логических элементах

Триггеры представляют собой логические устройства, предназначенные для запоминания логического состояния, установленного управляющими сигналами.

Состояние триггера, как правило, отражается выходами Q (потенциалом на выходе Q). Как правило, триггеры имеют парафазный выход, на выводах которого должно соблюдаться логическое соответствие.

Основными управляющими сигналами следует считать:

- сигнал S (set) – устанавливает в единичное состояние;

- сигнал R (reset) – сбрасывает триггер в нулевое состояние;

- сигнал C (clock) – сигнал, тактирующий работу триггера;

- сигнал D (DELTA) – вход данных для установки триггера;

- сигнал J (JUMP)

- сигнал K (KEEP)

- сигнал T (TIME) – счётный триггер

Активным уровнем входного сигнала могут быть как «высокий» так и «низкий». В последнем случае для обозначения активного уровня используется символ инверсии ( overline , overline ).

Простейшим видом триггера является R-S триггер, который можно реализовать на двух логических элементах.

При реализации триггера для управления могут использоваться как прямые сигналы, так и их инверсии, что отражает активный уровень их управляющего сигнала.

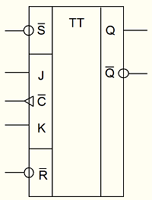

JK триггер

Микросхема типа К555ТВ9, является представителем семейства JK триггеров, который имеет следующий принцип работы.

Обозначение JK триггера К555ТВ9.

Микросхема К555ТВ9 содержит два JK триггера. Триггеры данного типа сложнее по устройству и по управлению по сравнению с RS триггером. В дополнение к стандартным входам R и S, которые работают аналогично с RS триггером, в JK триггере имеются информационные входа J и K, а также вход синхронизации С.

Таблица истинности JK триггера.

| Входы | Выходы | |||||

| -S | -R | C | J | K | Q | -Q |

| 0 | 1 | Х | Х | Х | 1 | 0 |

| 1 | 0 | Х | Х | Х | 0 | 1 |

| 0 | 0 | Х | Х | Х | Не определено | |

| 1 | 1 | 1→0 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1→0 | 0 | 1 | 0 | 1 |

| 1 | 1 | 1→0 | 0 | 0 | Не изменяется | |

| 1 | 1 | 1→0 | 1 | 1 | Меняется на противоположное | |

| 1 | 1 | 1 | Х | Х | Не изменяется | |

| 1 | 1 | 0 | Х | Х | Не изменяется | |

| 1 | 1 | 0→1 | Х | Х | Не изменяется | |

Принцип работы JK триггера следующий. Вход R триггера служит для перевода прямого выхода в лог.1, а вход S триггера – в состояние лог.0. Вход С (англ. Clock – часы)служит для тактирования JK триггера, то есть все изменения выходов происходят только когда на входе С сигнал изменяется с высокого уровня на низкий. Информационные входа J (англ. Jump – прыжок) и К (англ. Kill – убить) работают следующим образом: если на J лог.1 и на К лог.0, то по импульсу со входа С на Q будет лог.1 и на –Q будет лог.0. Для изменения уровня сигнала на выходах на противоположные необходимо на J подать лог.0, а на К лог.1, тогда по импульсу на входе С состояние выходов измениться.

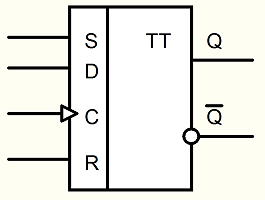

D триггер

D триггер является самым используемым, а по управлению он занимает промежуточное положение между RS триггером и JK триггером. Представителем D триггеров является микросхема К555ТМ2.

Обозначение D триггера микросхемы К555ТМ2

В составе данной микросхемы содержится два D триггера, которые имеют два входа сброса и установки R и C, информационный вход D (англ. Dalay – задержка) триггера и один тактируемый вход С триггера, а также два выхода: прямой Q и инверсный –Q. Как и все триггеры, у которых имеется тактируемый вход С, принцип работы D триггера основан на переключении уровней напряжений на выходе триггера только стробированием по входу С. Таким образом можно составить таблицу истинности D триггера.

Таблица истинности D триггера

| Входы | Выходы | ||||

| -S | -R | C | D | Q | -Q |

| 0 | 1 | X | X | 1 | 0 |

| 1 | 0 | X | X | 0 | 1 |

| 0 | 0 | X | X | Не определено | |

| 1 | 1 | 0→1 | 0 | 0 | 1 |

| 1 | 1 | 0→1 | 1 | 1 | 0 |

| 1 | 1 | 0 | Х | Не меняется | |

| 1 | 1 | 1 | Х | Не меняется | |

| 1 | 1 | 1→0 | Х | Не меняется | |

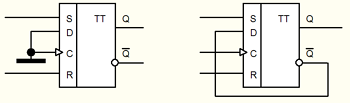

D триггер является наиболее универсальным потому, что данным триггером можно заменить все остальные RS триггеры и JK триггеры. Для замены RS триггера необходимо просто не использовать входы D и C входы D триггера, а относительно JK триггера, то для большинства схем одной пары входов вполне достаточно. Ниже приведены схемы замены триггеров

Схема замены D триггером: RS триггера (слева) и JK триггера в счётном режиме (справа).

Теория это хорошо, но необходимо отрабатывать это всё практически ПОПРОБОВАТЬ МОЖНО ЗДЕСЬ