После того как вы поделитесь материалом внизу появится ссылка для скачивания.

Получить код —>

Подписи к слайдам:

- арифметические;

- логические;

- операции над битами.

- Арифметической операцией называют процедуру обработки данных, аргументы и результат которой являются числами (сложение, вычитание, умножение, деление).

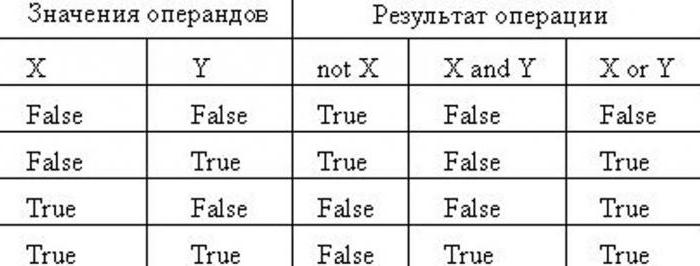

- Логической операцией именуют процедуру, осуществляющую построение сложного высказывания (операции И, ИЛИ, НЕ).

- Операции над битами обычно подразумевают сдвиги в битах.

История создания АЛУ

Разработчик компьютера ENIAC, Джон фон Нейман, был первым создателем АЛУ. В 1945 году он опубликовал первые научные работы по новому компьютеру, названному EDVaC (Electronic Discrete Variable Computer). Годом позже он работал со своими коллегами над разработкой компьютера для Принстонского института новейших исследований.

Архитектура этого компьютера позже стала прототипом архитектур большинства последующих компьютеров. В своих работах фон Нейман указывал устройства, которые, как он считал, должны присутствовать в компьютерах. Среди этих устройств присутствовало и АЛУ.

Фон Нейман отмечал, что АЛУ необходимо для компьютера, поскольку оно гарантирует, что компьютер будет способен выполнять базовые математические операции включая сложение, вычитание, умножение и деление.

АЛУ состоит из регистров, сумматора с соответствующими логическими схемами и элемента управления выполняемым процессом.

Устройство работает в соответствии с сообщаемыми ему именами (кодами) операций, которые при пересылке данных нужно выполнить над переменными, помещаемыми в регистры.

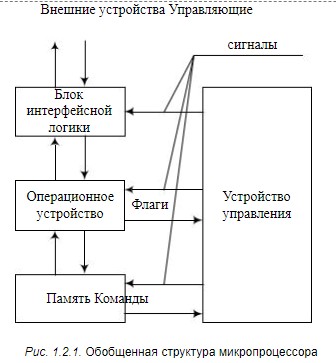

Арифметико-логическое устройство функционально можно разделить на две части:

- микропрограммное устройство (устройство управления), задающее последовательность микрокоманд (команд);

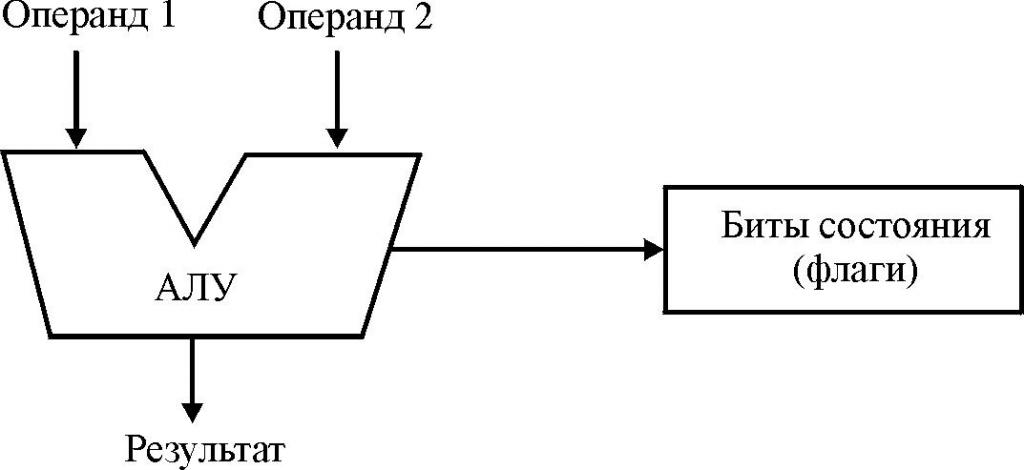

Структурная схема арифметико-логического устройства

По способу действия над операндами АЛУ делятся на последовательные и параллельные.

- в последовательных АЛУ операнды представляются в последовательном коде, а операции производятся последовательно во времени над их отдельными разрядами;

- в параллельных АЛУ операнды представляются параллельным кодом и операции совершаются параллельно во времени над всеми разрядами операндов.

По способу представления чисел различают АЛУ:

- для чисел с фиксированной точкой;

- для чисел с плавающей точкой;

- для десятичных чисел.

По характеру использования элементов и узлов АЛУ делятся на блочные и многофункциональные

Выполняемые в АЛУ операции можно разделить на следующие группы:

- операции двоичной арифметики для чисел с фиксированной точкой;

- операции двоичной (или шестнадцатеричной) арифметики для чисел с плавающей точкой;

- операции десятичной арифметики;

- операции индексной арифметики (при модификации адресов команд);

- операции специальной арифметики;

- операции над логическими кодами (логические операции);

- операции над алфавитно-цифровыми полями.

Современные ЭВМ общего назначения обычно реализуют операции всех приведённых выше групп, а малые и микроЭВМ, микропроцессоры и специализированные ЭВМ часто не имеют аппаратуры арифметики чисел с плавающей точкой, десятичной арифметики и операций над алфавитно-цифровыми полями. В этом случае эти операции выполняются специальными подпрограммами.

Видеоурок 3.39. Арифметико-логические устройства (АЛУ). Часть 1

К арифметическим операциям относятся сложение, вычитание, вычитание модулей («короткие операции») и умножение и деление («длинные операции»).

Группу логических операций составляют операции дизъюнкция (логическое ИЛИ) и конъюнкция (логическое И) над многоразрядными двоичными словами, сравнение кодов на равенство.

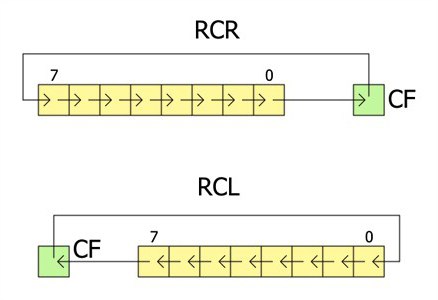

Специальные арифметические операции включают в себя нормализацию, арифметический сдвиг (сдвигаются только цифровые разряды, знаковый разряд остаётся на месте), логический сдвиг (знаковый разряд сдвигается вместе с цифровыми разрядами).

- Что такое операнд?

- Что такое элементарная операция?

- Что такое машинное слово?

Определение понятия

Арифметико-логическое устройство — один из блоков процессора, управляемый УУ (устройством управления). Его предназначение: выполнение логических и арифметических преобразований над данными-операндами (аргументами операции, информацией, обрабатываемой программой). Разрядность операндов в данном случае — размер или длина машинного слова.

Современное многофункциональное АЛУ состоит сегодня из двух частей:

- Операционное устройство.

- Устройство управления. Проводит вторичную дешифрацию кодов команды, определяет операцию, выполняемую в арифметико-логическом устройстве.

Набор выполняемых операций

Важно знать, какие операции должно исполнять АЛУ для того, чтобы обладать функциональной полнотой. Как правило, хватает четырех:

- Обращение к памяти устройства для чтения или записи информации.

- Декремент/инкремент.

- Сравнение. Здесь реализуется возможность условного перехода.

- Остановка функционирования устройства.

Если мы обратимся к первым арифметико-логическим устройствам, то увидим, что количество выполняемых ими операций ограничивалось 16-ю. Современные АЛУ способны выполнять сотни! Кстати, число операций и сегодня является важнейшей характеристикой данных устройств.

Арифметико-логические устройства. Определение, структура, подход к проектированию, основные уравнения работы алу (пример синтеза выражения). Особенности знаковой и беззнаковой арифметики.

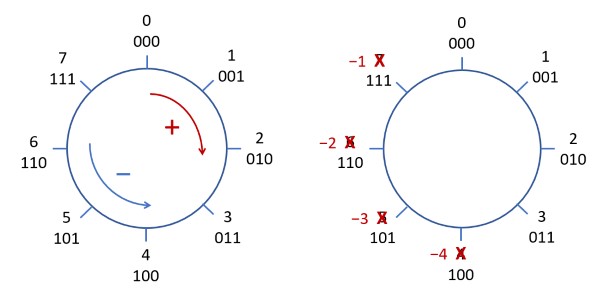

Особенностью цифровой арифметики является то, что она модульная, то есть ограничена некоторым максимальным числом, больше которого не существует. В данном случае модульная арифметика ограничена разрядностью цифрового устройства. Например, 3-битный сумматор не может выдать число, больше 111, то есть 7 в десятичной системе счисления. Можно сказать, что в такой арифметике не числовая прямая, а числовой круг. Операции сложения и вычитания — это движение по этому кругу в одну или в другую сторону. Благодаря особенностям такой арифметики можно выполнять вычитание используя операцию сложения. Выражение (A — B) эквивалентно выражению (A + ~B + 1). При этом к числам можно относиться либо как к беззнаковым (только положительным), либо как к знаковым (в таком случае старший бит числа указывает на знак, 1 — минус).

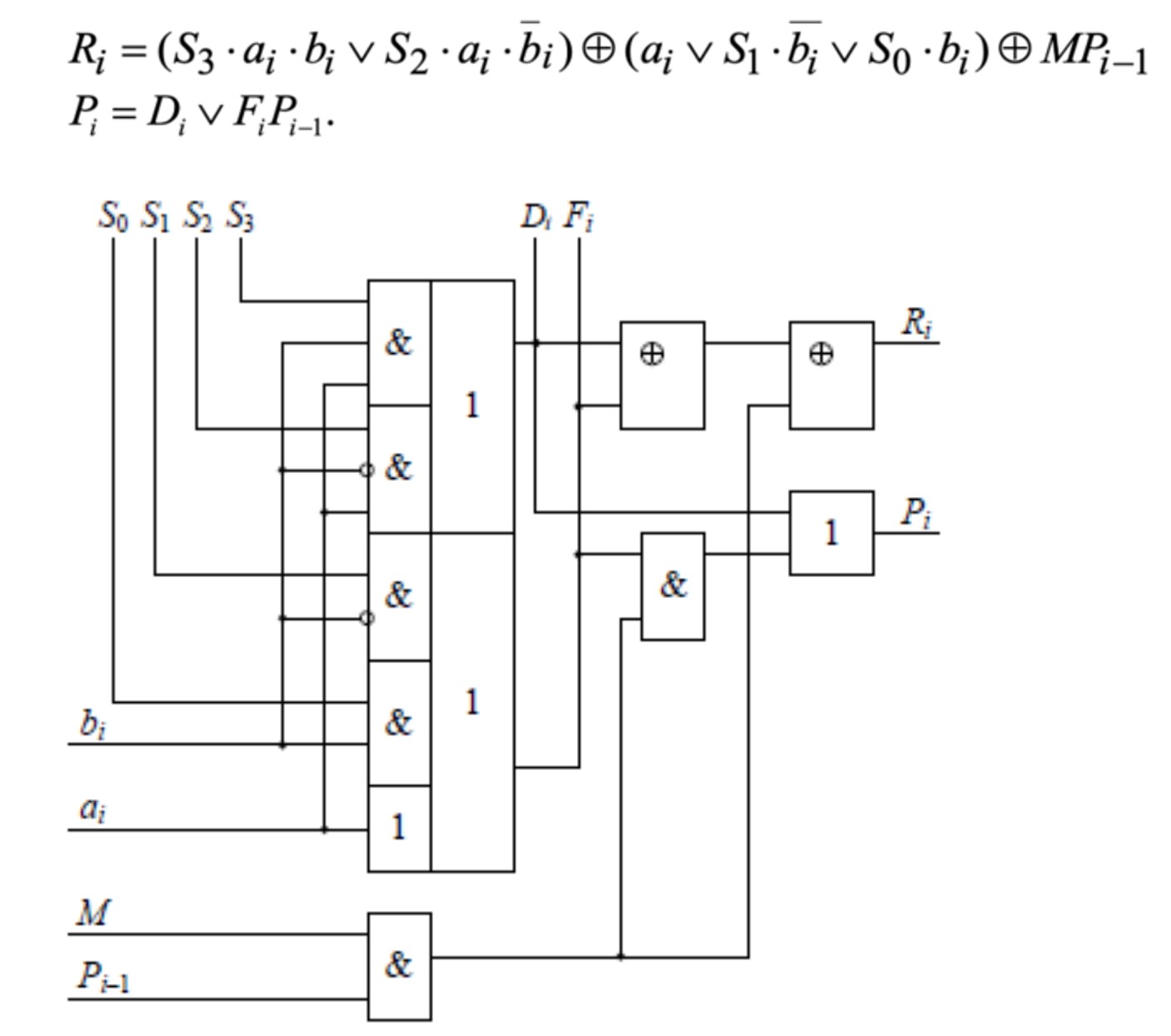

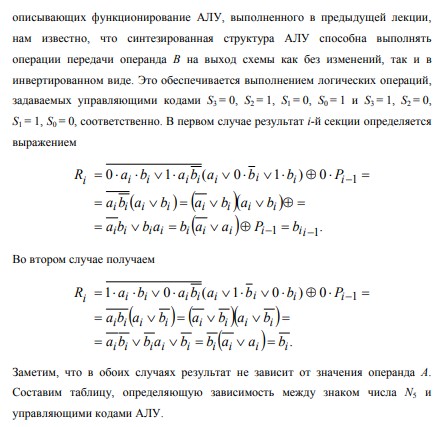

Уравнения АЛУ

S — управляющее слово, a, b — операнды, P — перенос, M — выключатель переноса, R — результат операции. Индексы внизу указывают на то, что выражение относится к отдельному i-ому биту результата.

Например, чтобы выполнить операцию A ИЛИ B, надо подать управляющие сигналы S = 0001, M = 0, тогда в выражении R сократятся импликанты с S3, S2, S1 и M, потому что они равны нулю, и останется только R = a | b.

Дополнительные пояснения к работе схемы:

АПС Л3. Цифровая арифметика. АЛУ (youtube.com)

Таймкод 1:15:20

3. Арифметико-логические устройства. Определение, структура, подход к проектированию. Вариант АЛУ на основе мультиплексирования операций. Схема ускоренного переноса. Особенности знаковой и беззнаковой арифметики.

АЛУ – это комбинационная схема, предназначенная для выполнения арифметических и поразрядно логических операций над многоразрядными словами.

Основные требования к АЛУ:

- выполнение арифметических и логических операций (разнообразие данных операций обеспечивает набор команд, которые сможет выполнять микропроцессор);

- обеспечение межразрядного переноса при выполнении арифметических операций

(от этого зависит быстродействие вычислительной системы);

- обеспечение наращивания разрядности обрабатываемых слов однотипными секциями.

Арифметико-логические устройства (АЛУ) представляют собой ключевую часть центрального процессора компьютера, ответственную за выполнение арифметических операций (сложение, вычитание, умножение, деление) и логических операций (И, ИЛИ, НЕ, сдвиги и т.д.).

Структура АЛУ включает в себя арифметический блок для выполнения операций с числами, логический блок для выполнения операций над битами и регистры для хранения данных и промежуточных результатов. АЛУ также содержит управляющие сигналы, которые определяют, какая операция будет выполнена.

При проектировании АЛУ учитываются требования к скорости выполнения операций, точности вычислений, набору поддерживаемых операций, а также возможности расширения функциональности. Проектирование включает выбор подходящих элементов (например, сумматоров, умножителей, логических элементов), определение структуры управления и оптимизацию для достижения наилучшей производительности при заданных ограничениях на мощность и площадь.

Общий подход к проектированию АЛУ включает в себя анализ требований к операциям, выбор подходящих алгоритмов и структур данных, оптимизацию производительности и проверку корректности работы на различных входных данных.

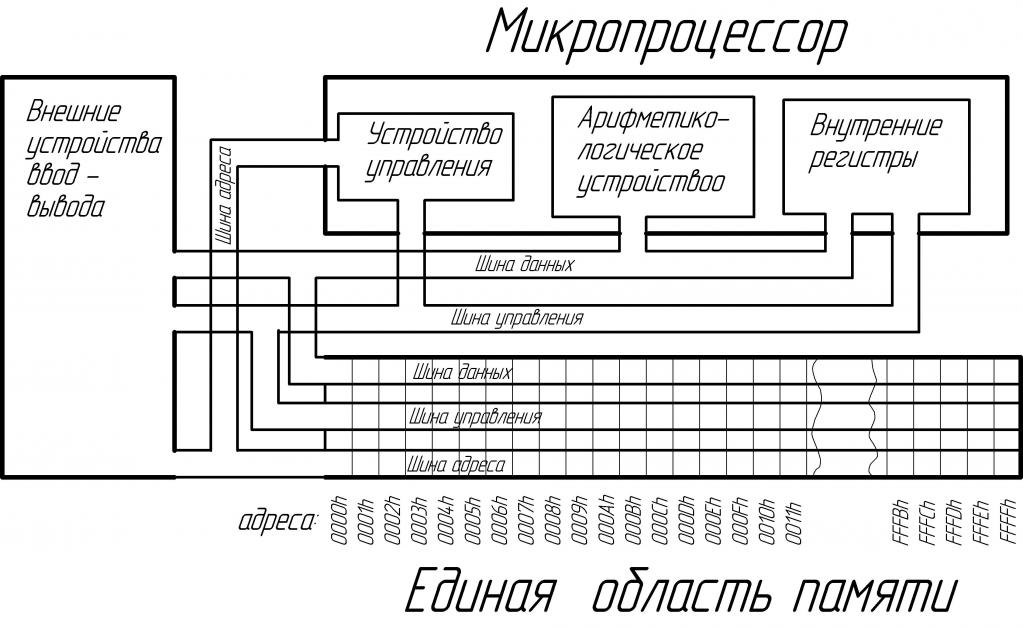

Вариант АЛУ на основе мультиплексирования операций: АЛУ (арифметико-логическое устройство) на основе мультиплексирования операций представляет собой конструкцию, в которой один блок управления выбирает тип операции (например, сложение, вычитание, умножение, деление) на основе внешних сигналов управления. Это позволяет сократить количество физических элементов и уменьшить потребление энергии.

Схема ускоренного переноса: Схема ускоренного переноса, также известная как алгоритм Carry Look-Ahead (CLA), является методом, используемым в цифровых схемах арифметики для ускорения вычислений переносов при операциях сложения и вычитания. Обычно при выполнении этих операций перенос от одного разряда к другому может вызвать задержку, тормозящую скорость операции. Однако с использованием схемы ускоренного переноса эта задержка уменьшается.

Этот метод основан на разбиении задачи управления переносами на обработку групп разрядов параллельными шагами. В отличие от обычного метода, где следующий перенос зависит от предыдущего, в схеме ускоренного переноса каждый разряд вычисляет переносы независимо от других.

Это достигается за счет предварительного вычисления «производных» переносов для каждой пары разрядов без учета их собственных значений. Это позволяет аппаратуре одновременно генерировать переносы для всех разрядов, независимо от значений самих разрядов, что значительно ускоряет процесс. Она эффективно обрабатывает переносы между разрядами, ускоряя выполнение арифметических операций.

Особенности знаковой и беззнаковой арифметики: В знаковой арифметике числа представлены со знаком, что позволяет учитывать положительные и отрицательные значения. В беззнаковой арифметике числа интерпретируются как исключительно положительные, и отсутствует возможность представления отрицательных чисел.

Арифметико-логическое устройство

Аннотация: Рассматриваются особенности реализации арифметико-логического устройства компьютера на примере проектирования АЛУ для умножения чисел с фиксированной запятой, заданных в прямом коде, со старших разрядов множителя.

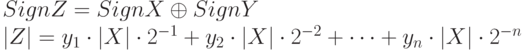

Классическая ЭВМ состоит из трех основных устройств: арифметико-логического устройства , устройства управления и запоминающего устройства. Рассмотрим особенности организации этих устройств. Прежде всего, рассмотрим структуру арифметико-логического устройства .

В современных ЭВМ арифметико-логическое устройство не является самостоятельным схемотехническим блоком. Оно входит в состав микропроцессора, на котором строится компьютер . Однако знание структуры и принципов работы АЛУ весьма важно для понимания работы компьютера в целом. Для лучшего понимания этих вопросов проведем синтез арифметического устройства, предназначенного для выполнения только одной операции – умножения чисел с фиксированной запятой , заданных в прямом коде, со старших разрядов множителя [13] . В ходе этого процесса также обратим внимание на особенности использования рассмотренных выше основных схемотехнических элементов ЭВМ.

Синтез АЛУ проходит в несколько этапов. Сначала необходимо выбрать метод, по которому предполагается выполнение операции , и составить алгоритм соответствующих действий. Исходя из алгоритма и формата исходных данных, следует определить набор составляющих АЛУ элементов. Затем требуется определить связи между элементами, установить порядок функционирования устройства и временную диаграмму управляющих сигналов, которые должны быть поданы на АЛУ от устройства управления.

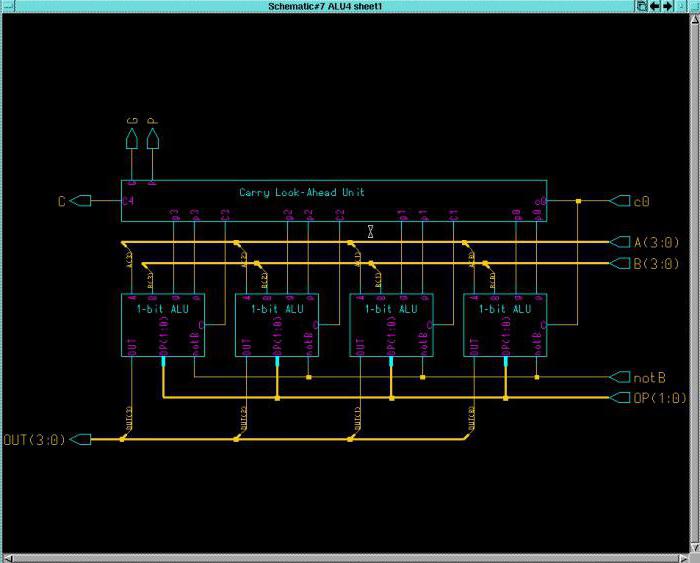

Пусть операнды имеют вид:

[X]пк = x0x1x2…xn [Y]пк = y0y1y2…yn

где x0 , y0 – знаковые разряды.

Операция умножения чисел с фиксированной запятой , заданных в прямом коде, со старших разрядов множителя выполняется по следующей формуле:

![[X]_</p><p>= 0.1101; Sign X = 0 \ [Y]_ = 1.1011; Sign Y = 1 \ Sign Z = 0 oplus 1 = 1 \ |X| = 0. 1 1 0 1 \ |Y| = 0. 1 0 1 1 \ y_y_y_y_ \ +0.00000000 |Z| = 0 \ y_ = 1 0.01101000 1 cdot |X| cdot 2^ \ + ovwerline |Z| = |Z| + |X| cdot 2^ \ y_ = 0 0.00000000 0 cdot |X| cdot 2^ \ + overline |Z| = |Z| + 0 \ y_ = 1 0.00011010 1 cdot |X| cdot 2^ \ + overline |Z| = |Z| + |X| cdot 2^ \ y_ = 1 0.00001101 1 cdot |X| cdot 2^ \ overline |Z| = |Z| + |X| cdot 2^](https://intuit.ru/sites/default/files/tex_cache/7af37921efed33c4bbe7f79df3e492e3.png)

Алгоритм вычислений представлен на рис. 3.1

Рис. 3.1. Алгоритм операции умножения чисел с фиксированной запятой, заданных в прямом коде, со старших разрядов множителя

Каждой переменной, представленной в алгоритме, в схеме должен соответствовать элемент хранения. Разрядность модуля произведения равна сумме разрядностей сомножителей. Умножение двоичного числа на 2 -i обеспечивается сдвигом этого числа вправо на соответствующее количество разрядов. Переход к анализу очередного разряда множителя ( i = i + 1 ) может быть обеспечен сдвигом регистра множителя на один разряд в сторону старших разрядов.

Исходя из этого, определим состав оборудования, необходимого для реализации АЛУ заданного типа для n = 4 ( таблица 3.1).

| Регистр модуля множимого RGX | 8 | Загрузка. Сдвиг в сторону младших разрядов. | УС1 УС2 |

| Регистр модуля множителя RGY | 4 | Загрузка. Сдвиг в сторону старших разрядов. | УС3 УС4 |

| Регистр модуля результата RGZ | 8 | Загрузка. Установка в » 0 «. | УС5 УС6 |

| Триггер знака множимого TX | Загрузка | УС7 | |

| Триггер знака множителя TY | Загрузка | УС8 | |

| Триггер знака результата TZ | Загрузка | УС9 | |

| АЛУ | 8 | Комбинационный сумматор | – |

| Комбинационные схемы | Получение на входе АЛУ сигналов » 0 » или RGX в зависимости от значения yi | – |

Структурная схема устройства представлена на рис. 3.2.

Основные функции

Арифметико-логическое устройство является составной частью процессора компьютера. АЛУ будет выполнять следующие функции:

- Двоичной арифметики для информации в форматах с фиксированной точкой.

- Двоичной арифметики для информации в форматах с плавающей точкой.

- Арифметики двоично-десятичного представления сведений.

- Логические операции (арифметические и логические сдвиги).

- Пересылка информации.

- Работа с символьными данными.

- Работа с графической информацией.

Главные количественные характеристики

Составные части арифметико-логического устройства (ОУ и УУ) определяют количественные характеристики всей системы АЛУ. В частности, это следующее:

- Время выполнения одной операции.

- Скорость выполнения операций вообще.

- Число исполняемых операций.

- Точность предоставленной информации.

Операции устройства

Структура АЛУ предполагает выполнение действий через логические функции, которые делятся на такие группы:

- десятичная арифметика;

- двоичная арифметика для цифр с четко обозначенной точкой;

- шестнадцатеричная арифметика для выражений с плавающим разделителем;

- модификация адресов команд;

- операции логического типа;

- преобразование алфавитно-цифровых полей;

- специальная арифметика.

Современные электронно-вычислительные машины способны реализовать все вышеупомянутые типы активности, а микроЭВМ не имеют такого базового функционала, поэтому наиболее сложные процедуры выполняют через подключение небольших подпрограмм.

Арифметические операции и логические процедуры

Все действия АЛУ можно условно разделить на несколько групп.

Арифметические операции включают в себя деление, умножение, вычитание модулей, обычное вычитание и сложение.

К группе логических преобразований причисляют логическое «и» и «или», то есть конъюнкцию и дизъюнкцию, а также сравнение данных на равенство. Такие процедуры, как правило, проводят над двоичными словами, состоящими из множества разрядов.

К специальным арифметическим операциям относятся нормализация, логический и арифметический сдвиги. Между этими преобразованиями есть существенная разница. Если при арифметическом сдвиге в местоположении меняют лишь цифровые разряды, то при логическом знаковый разряд присоединяется к движению.

Каждую операцию, которая происходит посредством использования арифметико-логического устройства, можно назвать последовательностью функций логического типа, которые описываются многоразрядной логикой для электронно-вычислительных машин. К примеру, для двоичных ЭВМ используется двоичная логика и так далее, вплоть до десятеричной системы.

Абсолютно у всех арифметико-логических преобразований есть собственные операнды, а результаты на выходе трактуются как битовые строки с шестнадцатью разрядами. Исключением являются лишь примитивы знакового деления DIVS. А разнообразные флаги позволяют трактовать данные на выходе как цифры со знаком минус или плюс при переполнении. Логика преобразования битов строится на арифметике по модулю. Флаг ставится, если произошли непредсказуемые изменения со знаком. К примеру, складывая два положительных числа, вы должны получить результат со знаком «+». Но если происходит перенос в знаковый бит, устанавливающий единицу, а итог получается отрицательным, то устанавливается флаг переполнения.

Логика бита переноса базируется на беззнаковой арифметике. Этот флаг устанавливается системой, если сгенерированный перенос из старшего разряда не может быть записан как результат. Этот бит АЛУ очень эффективен при использовании преобразований с многословными представлениями.

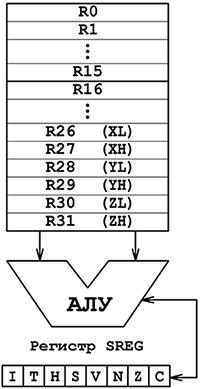

Арифметико-логическое устройство

Арифметико-логическое устройство (АЛУ) выполняет все вычислительные операции в микропроцессорной системе. Непосредственно к АЛУ подключены 32 РОНа (регистровый файл), как показано на рис.8.

Рис.8 Арифметико-логическое устройство В большинстве операций любой из этих регистров может использоваться в качестве источника входных данных либо приемника результата. При этом все арифметические и логические команды над РОНми имеют вид подобный add Rd,Rs. За названием мнемоники, которая описывает действие (addition – сложение), следуют два параметра (операнда). В данном случае это регистры Rd (destination – приемник) и Rs (source – источник), содержимое которых необходимо сложить между собою. Сумма будет размещена по адресу регистра Rd. Таким образом, сложить любые два регистра можно двумя разными способами: add R16,R17 (сложить R16 с R17 и поместить сумму в R16) или add R17,R16 (сложить R17 с R16 и поместить сумму в R17). Причем выборка содержимого регистров, сложение и сохранение результата займет всего 1 период тактовой частоты. Что касается, арифметических и логических действий над регистром и константой, то в целом они подобны действиями между РОНми. Однако в этих целях могут использоваться только старшая половина регистрового файла. Например, в команде вычитания константы из регистра subi Rd,K в качестве Rd могут выступать только регистры R16…R31. В состав АЛУ микроконтроллеров семейства ATmega входит также 2-тактный аппаратный умножитель 8×8 бит, который способен работать как с беззнаковыми так и со знаковыми числами представленными в дополнительном коде. Во всех разновидностях операции умножения, 16-разрядное произведение помещается в регистры R1 (старший байт) и R0 (младший байт). Регистры R26…R31 у AVR имеют двойное предназначение. Они могут быть использованы как три 16-разрядных указателя, которые имеют символьные имена X (XH:XL = R27:R26), Y (YH: YL = R29:R28), Z (ZH: ZL = R31:R30) и применяются для задания адресов ячеек SRAM в различных командах пересылки данных (ld Rd,X/Y/Z, st X/Y/Z,Rd и т.д.). Указатель Z, кроме этого, необходим инструкциям lpm/spm при чтении/записи FLASH-память программ. Регистры X и Y отсутствуют в некоторых устаревших моделях ATtiny. АЛУ любого микропроцессора неразрывно связано с регистром флагов программы (регистр состояния программы), который у AVR имеет название SREG (Status Register) и расположен в пространстве РВВ. Описание битов SREG приведено в табл.4. Все флаги SREG доступны как для чтения, так и для записи. Табл.4. Флаги регистра состояния программы SREG:

| Номер бита в регистре | Название флага | Описание |

| 0 | C | Флаг переноса. Устанавливается в 1 если в результате операции произошел выход за границы байта. |

| 1 | Z | Флаг нуля. Устанавливается в 1 если результат операции равен нулю. |

| 2 | N | Флаг отрицательного результата. В этот флаг копируется содержимое 7-мого MSB результата операции. |

| 3 | V | Флаг переполнения в дополнительном коде. Устанавливается в 1 при переполнении разрядной сетки знакового результата. |

| 4 | S | Флаг знака. Содержимое флага определяется как N XOR V. |

| 5 | H | Флаг половинного переноса. Устанавливается в 1 если в результате операции сложения/вычитания произошел перенос/заем из 3-тего бита в 4-тый. |

| 6 | T | Флаг хранения копируемого бита. Флаг используется в качестве источника и приемника командами копирования битов bld и bst соответственно. |

| 7 | I | Флаг глобального разрешения прерываний. При установке в 1 этого флага происходит разрешение всех немаскируемых прерываний. |

Флаг Z является показателем нулевого результата во всех вычислительных операциях. Флаги С и H используются преимущественно для связи байтов в процессе сложения/вычитания (флаг С также в сдвиговых операциях). Биты N,S и V необходимы для знаковых вычислений. Флаг T – источник и приемник в командах копирования битов bld/bst, но может быть использован и как дополнительная ячейка для хранения любой пользовательской информации (флаг пользователя). Последний флаг I, в отличие от всех остальных, не связан с результатами вычислительных операций либо операций пересылок и предназначен для глобального разрешения/запрета прерываний. Перейти к следующей части: Стек

Теги:

Котов Игорь Юрьевич

Котов Игорь Юрьевич  Опубликована: 2012 г.

Опубликована: 2012 г.  0

0  0

0

![]()

Вознаградить Я собрал 0 0

Вознаградить Я собрал 0 0